# FAQs on the Counter/Timer features of KPCI-3108 or KPCI-3107

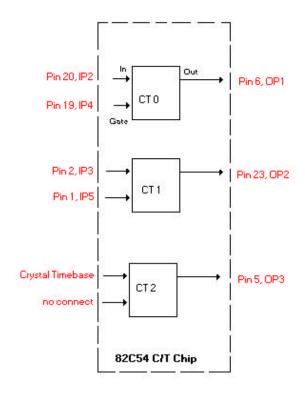

Below is a block diagram of the counter timer used on the KPCI-3108 or KPCI-3107:

Counter/Timer Sub-System of KPCI-3108 or KPCI-3107

#### **Architecture:**

The 82C54 chip provides three 16bit counters: CT0, CT1 and CT2. DriverLINX assigns the following logical channels to these counters:

Channel 0: 32bit cascade of CT1 and CT2

Channel 1: CT0 Channel 2: CT1 Channel 3: CT2

### **Connections:**

For C/T functions that use inputs, such as event counting, simply connect to the correct IPx pin number corresponding to the selected channel.

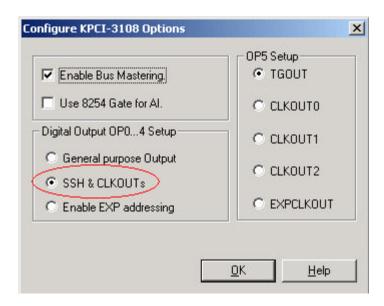

For C/T output functions, such as Square Wave Generation, the OPx must be configured in the DriverLINX Configuration Panel to serve as CT outputs. Access this from the 'Special Button' on the Device tab for your assigned device number (see below).

In each case, the IPx or OPx terminals are no longer available for their default role as digital inputs or outputs if in use for C/T functions.

# **Crystal Timebase Values**

The value of the timebase is software selectable:

INTERNAL1: corresponds to the setting in the DriverLINX Configuration Panel (default is 5MHz)

INTERNAL2: 10 MHz INTERNAL3: 5 MHz INTERNAL4: 1 MHz INTERNAL5: 100 KHz

### **Use Considerations**

When performing paced Analog Input, logical channel 0 of the CT sub-system will be used by default. This means that only CT0, logical channel 1, would still be available for other tasks.

However, a CT channel other than the default 32bit cascaded channel could be selected for the pacing source for the Analog Input task to increase the number of counters available for other tasks. The only consequence to the Analog Input task would be a reduction in the range of pacing frequencies available with a single 16bit counter relative to 32bit cascaded channel.

See the Counter/Timer Channel Usage section of the 'Using DriverLINX with your KPCI-3108 Series Hardware' manual for more information.